2024年初,研究机构普遍预计谷底已过,市场将迎来增长,整体规模将增至6000亿美元以上。现实情况略有偏差,市场确实实现了超过6000亿美元的增长,但这主要表现为人工智能对半导体产品需求的拉动,而传统的消费电子、智能手机、汽车等需求仍然不足。反映到供应链上就表现为,先进制程供不应求,成熟制程面临过剩,使得市场的增长只惠及到了少数芯片大厂,多数中小企业依然在与弱市、库存做斗争。

预计2025年,芯片制造领域的表现仍将呈现两极分化,近来不断有关于争夺台积电5nm/4nm与3nm产能的消息传出,就证明了这一点。而2025年芯片制造领域最受关注的可能就是2nm工艺的量产,以及围绕于此的芯片制造大厂间的角力。

2025年大厂角力2nm

2nm是半导体制造领域一次重大的工艺节点演进。三大芯片制造厂均选择在这一节点上引入了GAA(全环绕栅极)架构。相比传统的FinFET架构,GAA通过全方位包裹晶体管的栅极,实现了对电流的更精确控制,同时允许在相同的芯片面积内集成更多的晶体管,从而提升了芯片的密度和性能。这对于需要高性能、低功耗的应用场景尤为重要。

目前,全球芯片制造大厂台积电、英特尔、三星均将2nm工艺节点的量产时间放在2025年。按照台积电的规划,2nm芯片将于2025年量产,A16(1.6nm)工艺将于2026年推出。有消息称,目前台积电的试产良率已超过60%。产能方面,台积电在高雄楠梓科学园区兴建的2nm晶圆一厂和晶圆二厂,预计分别于2025年第一季度和第三季度投产。市场方面,业界对2nm表现出旺盛需求。苹果有望成为首批客户,iPhone 18 Pro的A20 Pro处理器将采用台积电2nm制程生产。英特尔、AMD、高通、联发科等也有意加快导入速度。

英特尔也宣布,Intel 18A将于2025年开始量产,AI PC客户端处理器Panther Lake和服务器处理器Clearwater Forest都将采用Intel 18A工艺。另有采用Intel 18A的首家外部客户(外界猜测为博通)也将在2025年上半年完成流片。三星电子也在加快建设用于量产2nm工艺的生产设施。据报道,相关设备已引入位于三星华城工厂的“S3”代工线。三星的计划是到2025年第一季度安装一条月产能为7000片晶圆的生产线。三星还计划在平泽二厂的“S5”安装一条1.4nm生产线,到2027年大规模生产1.4nm,以追赶台积电。

英特尔押注Intel 18A工艺,这是其在半导体制造领域与台积电角力,重新争夺先进工艺话语权的关键一战。此前英特尔制定了雄心勃勃的“五年,四个节点(5Y4N)”路线图,Intel 18A是其中最先进的节点,也是英特尔的倾心之作,被寄予厚望。英特尔在Intel 18A工艺中引入了RibbonFET全环绕栅极晶体管架构和PowerVia背面供电技术。PowerVia技术将电源线移动到晶圆背面,优化了信号路由,进一步降低了电阻,提高了能效。许多分析师认为其能够与台积电的先进工艺相抗衡,甚至有可能在市场上实现反超。

在这场技术角力中,英特尔的成败不仅关系到自身的未来发展,也将对整个半导体的产业格局产生影响。如果英特尔能够成功实现Intel 18A工艺的商用化,并借此夺回先进工艺的话语权,那么它将有望在全球半导体市场中重新占据一席之地,并开启一个全新的AI计算时代。

对台积电来说,这也是守住领先地位的关键一仗。如前所述,2nm在架构上的创新,晶体管密度的极大提升,是对材料科学、光刻技术、良率控制等多方面综合能力的极限考验。直接关系到台积电能否继续保持其在高端芯片制造领域的霸主地位。

为埃米时代布局

芯片大厂同时也在布局2nm之后的下一代CFET架构工艺技术。在近日召开的IEDM 2024(2024年IEEE国际电子器件会议)上,英特尔代工展示了栅极长度为6纳米的硅基RibbonFET CMOS晶体管,大幅缩短了栅极长度和减少沟道厚度,同时大幅抑制短沟道效应,持续缩短栅极长度是摩尔定律演进的一个关键指标。此外,英特尔代工还展示了减成法钌互连技术、选择性层转移、2D GAA晶体管的栅氧化层等新的技术进展。这些技术将从材料、异构集成等方面促进晶体管和互连微缩技术的突破。

台积电发表了《首次演示48nm栅极间距单片CFET反相器,面向未来逻辑技术扩展》的论文,介绍了在48nm栅极间距上制造的全功能单片CFET反相器的性能。CFET被认为是GAA之后的新一代晶体管架构。

IMEC发表《双排CFET:面积高效A7技术节点的设计技术协同优化》的研究,介绍了在z方向和x-y平面上继续将CFET扩展到更高的尺寸方面取得的进展。IMEC指出,双列CFET架构的主要好处在于简化制程和大幅减少逻辑元件和SRAM的面积。根据DTCO的研究,与传统的单列 CFET 相比,新架构能让标准单元高度从4轨降到3.5轨。A7或7埃米技术节点预计将遵循1nm(A10)节点技术。IMEC的路线图曾计划让CFET在2032年左右进入A5(0.5nm)节点的主流生产。

IBM和三星也参与了CFET探索,论文《面向未来逻辑技术的具有阶梯式通道的单片堆叠FET》,提出了阶梯式结构的概念,其中底部FET通道比上方的通道更宽。这样做的好处是堆叠高度降低,高纵横比工艺带来的挑战更少。论文还讨论了顶部-底部通道中间介电隔离、顶部-底部源极/漏极隔离和双功函数金属。

先进封装热点技术不断

芯片制造大厂对先进封装的关注度也在提升。在研究机构TechInsights对2025年的展望中,列举了中介层、芯粒(Chiplet)、面板级封装、硅光子、玻璃基板等热点技术。TechInsights表示,先进封装将继续影响半导体设计和制造工艺,有助于在降低成本的同时优化功耗、性能和面积(PPAC)。

人工智能的采用带动了高性能处理器与HBM封装的需求,进而增加了对硅中介层的需求。目前中介层是高性能封装的首选方法。台积电在11月举办的欧洲开放创新平台(OIP)论坛上宣布,有望在2027年认证其超大版本的CoWoS封装技术。该技术将提供高达9个掩模尺寸的中介层尺寸和12个HBM4内存堆栈,推进人工智能和HPC芯片的设计。

芯粒技术方面,英特尔代工在IEDM 2024上展示了选择性层转移技术。这是一种异构集成解决方案,能够以更高的灵活性集成超薄芯粒,与传统的芯片到晶圆键合(chip-to-wafer bonding)技术相比,选择性层转移让芯片的尺寸能够变得更小,纵横比变得更高。这项技术还带来了更高的功能密度,并可结合混合键合(hybrid bonding)或融合键合(fusion bonding)工艺,提供更灵活且成本效益更高的解决方案,封装来自不同晶圆的芯粒,为AI应用提供了一种更高效、更灵活的架构。

硅光/CPO共封装的进展也值得关注。台积电在IEDM 2024上发表的论文展示了硅光CPO集成技术的进展,介绍了一种用于宽带光引擎应用的EIC/PIC Chiplet集成的技术。新工艺流程实现了多行集成。与传统的宽带端面耦合器(EC)不同,当每行集成40到80根光纤时,该解决方案不受边缘翘曲问题的影响。

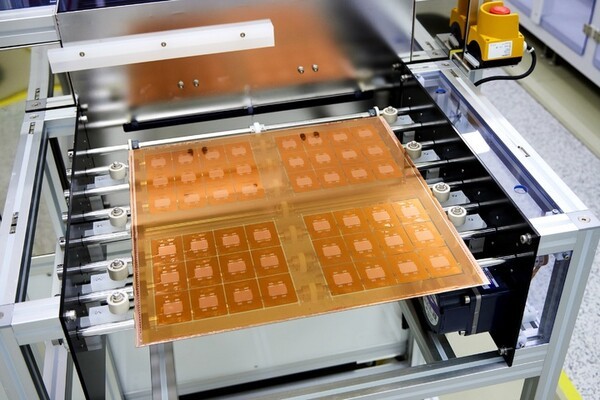

面板级封装方面,台积电预计将于2027年开始生产。英伟达和三星等公司已采用FO-PLP技术。不过FO-PLP仍面临面板翘曲、均匀性、成本及良率等挑战,其广泛的市场应用仍待时日。

至于玻璃基板的研发,英特尔、AMD、三星、SK海力士等公司均在推动。英特尔是最早行动的公司之一,计划在2026年大规模量产玻璃基板,并已在美国亚利桑那州设立专门研究机构。AMD跟进这一行业趋势,计划最早于2025年开发出采用玻璃基板的芯片,目前已开始对供应商提供的玻璃基板样品进行测试。三星电机也已启动玻璃基板研发及生产,测试产线预计将于2025年建成。SK海力士通过其美国子公司Absolics在佐治亚州投资3亿美元开发专用生产设施,计划在2025年实现量产原型基板。